# **Topologies for High-Speed Drives**

Giorgo Kapino 27-06-2019

**SDU Electrical Engineering**

## Background

Giorgo Kapino

Ph.D. student in Power Electronics, Centre for Industrial Electronics – SDU

M.Sc. in Electronics, University of Southern Denmark

B.Sc. In Electrical Engineering, Technological Educational Institute of Central Greece

#### Topic: "Topologies for High-Speed Drives"

## Overview

# Motivation for High-Speed Drives

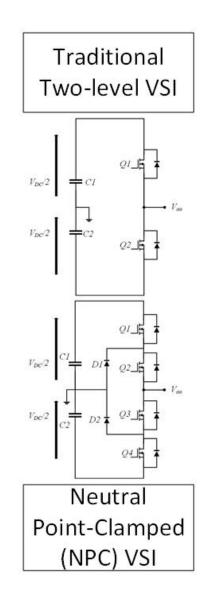

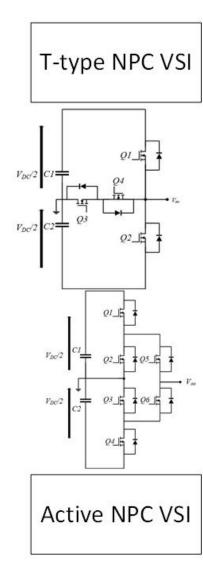

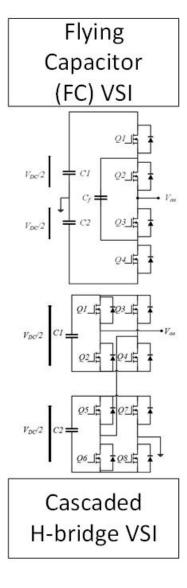

# Topologies

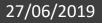

# Efficiency comparison

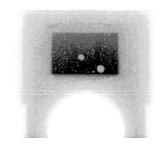

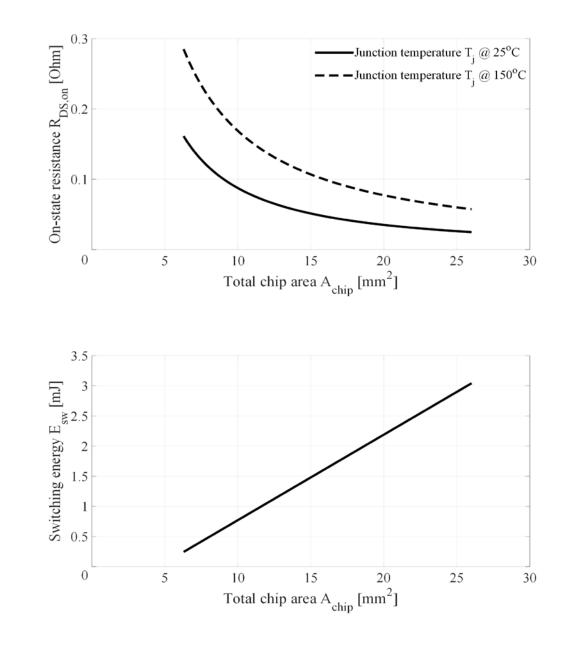

# SiC die area characterization

#### Rohm's SCT3030KL Cree's C2M0025120D

# SiC die area characterization

## Future plan

Algorithm for iterative SiC chip area comparison

Prototype design

Filter design for high-speed drives

650V-900V SiC chip area characterization database

18

## Thank you for your time. Questions?

## Giorgo Kapino

### Ph.D. student

## Email: <a href="mailto:gkapino@mci.sdu.dk">gkapino@mci.sdu.dk</a>

## Telephone: +45 65 50 7640